题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

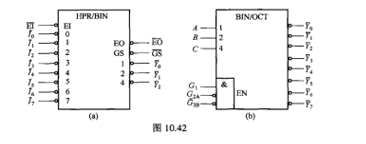

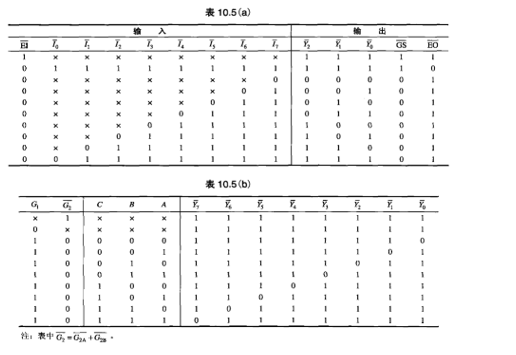

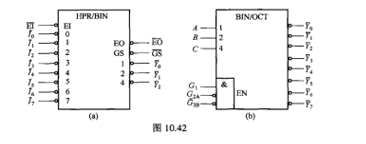

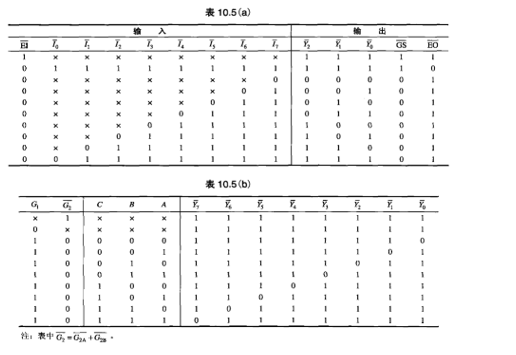

74148的逻辑符号和功能表分别如图10.42(a)和表10.5(a)所示,74138的逻辑符号和功能表分别如图10

.42(b)和表10.5(b)所示.试用1片二进制优先编码器74148、1片二进制译码器74138和少量与门设计一个8-3格雷码编码器.要求写出设计过程,画出电路图(3位二进制码A2A1A0和对应格雷码B2B1B0之间的关系为B2=A2其他 ).

).

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

.42(b)和表10.5(b)所示.试用1片二进制优先编码器74148、1片二进制译码器74138和少量与门设计一个8-3格雷码编码器.要求写出设计过程,画出电路图(3位二进制码A2A1A0和对应格雷码B2B1B0之间的关系为B2=A2其他 ).

).

更多“74148的逻辑符号和功能表分别如图10.42(a)和表10…”相关的问题

更多“74148的逻辑符号和功能表分别如图10.42(a)和表10…”相关的问题

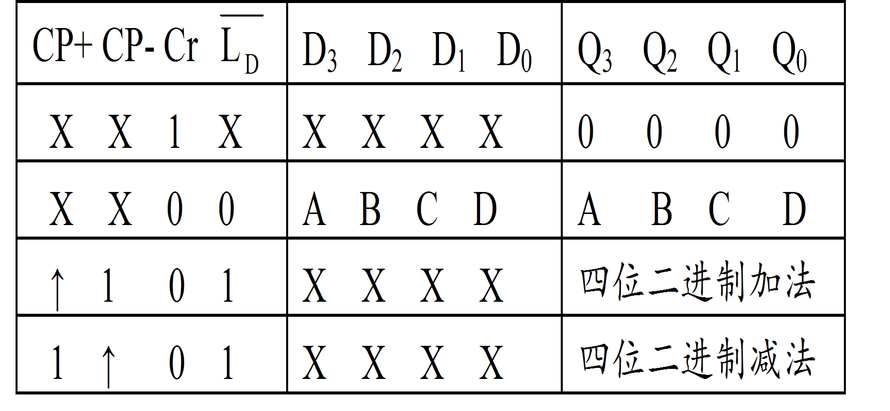

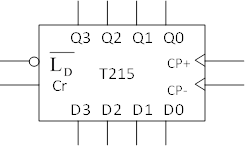

(14分)已知T215计数器的功能表及简化的逻辑符号分别如表5和图5.a所示。 表5 T215计数器功能表 图5.a

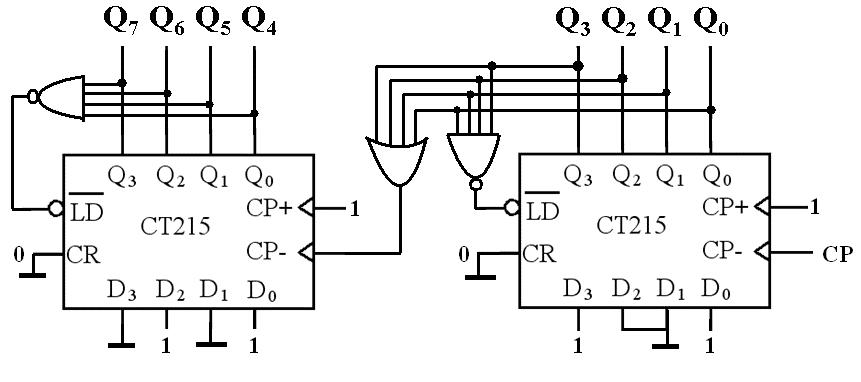

图5.a 1、用T215和最少的门组成一个8421BCD码的九进制减法计数器。 2、用T215和最少的门组成一个40进制加法计数器(8421BCD编码)。 3、分析由两片T215计数器构成的图5.c所示电路的功能是:()进制、()法计数器、采用()编码。 图5.c

1、用T215和最少的门组成一个8421BCD码的九进制减法计数器。 2、用T215和最少的门组成一个40进制加法计数器(8421BCD编码)。 3、分析由两片T215计数器构成的图5.c所示电路的功能是:()进制、()法计数器、采用()编码。 图5.c

用同步二进制加法计数器74161(逻辑符号及功能表见附录)和一个3-8线译码器74138以及门电路设计一个具有开机消零功能的模7计数器,要求计数器按下列规律计数,要求写出设计过程,画出电路图:

0,4,9,12,3,6,9,0,4,…

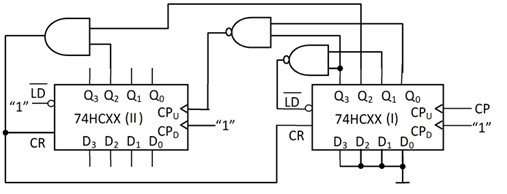

某中规模集成计数器74HCXX的功能表和简化逻辑符号如下所示。 用该集成计数器连接而成的电路如下图所示。该电路是 (同步/异步)、 (加法/减法)计数器;其中74HCXX(I)片连接成 进制计数器;整个电路是 进制计数器。(答案间用中文分号隔开)

用该集成计数器连接而成的电路如下图所示。该电路是 (同步/异步)、 (加法/减法)计数器;其中74HCXX(I)片连接成 进制计数器;整个电路是 进制计数器。(答案间用中文分号隔开)

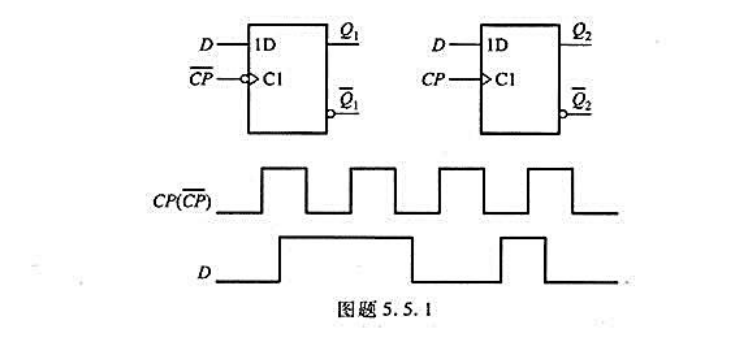

上升沿触发 和下降沿触发的D触发器逻辑符号及时钟信号CP( )和输入信号D的波形如图题5.5.1所示。分别画出它们的Q端波形。设触发器的初始状态为0。

)和输入信号D的波形如图题5.5.1所示。分别画出它们的Q端波形。设触发器的初始状态为0。

设某三位二进制译码器的功能表如下所示,则写出利用此译码器的输出实现如下逻辑功能的逻辑式: (1) (2)

(2)

X1X0、Y=Y1Y0的数据比较器.当X≥Y时输出Z=1,否则Z=0.要求:

(1)简要给出设计步骤;

(2)画出逻辑电路图.

图1中所示是8线-3线优先编码器74148的逻辑符号,其功能表如表3-5所示。试用以构成一个16线-4线优先编码器。

表3-5 8线-3线优先编码器的功能表

|

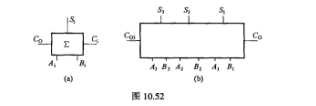

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其

中G=Ai·Bi,P=Ai+Bi),试求采用超前进位结构的三位二进制加法器(如图10.52(b)所示)的最高位进位输出表达式Co3.

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

简答题

简答题

微信搜一搜

微信搜一搜

简答题

简答题