题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设计一个能存放8位二进制代码的寄存器,需要由( )个触发器构成。

A.8

B.4

C.3

D.2

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.8

B.4

C.3

D.2

更多“设计一个能存放8位二进制代码的寄存器,需要由()个触发器构成…”相关的问题

更多“设计一个能存放8位二进制代码的寄存器,需要由()个触发器构成…”相关的问题

当A3=0时,触发器E清零,计数器继续计数。

当A3=1时,触发器E置1,并检测A4,A4=0时,继续计数;A4=1时,触发器F置1,并停止计数,回到系统初始状态。

(1)试画出该系统的ASM图

(2)画出该系统控制单元的状态图,并用D触发器及必要的门电路设计控制单元

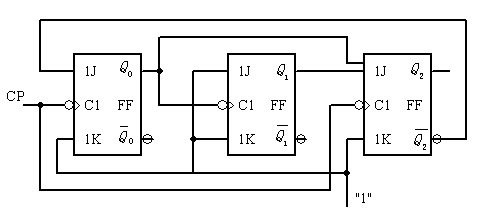

A、不具有自启动能力的六进制计数器

B、具有自启动能力的六进制计数器

C、具有自启动能力的五进制计数器

D、不具有自启动能力的七进制计数器

要求写出设计过程,并画出连接图.

(1)画出系统的ASM图。

(2)画出系统的状态转换图。

(3)用Verilog HDL语言描述其工作过程。

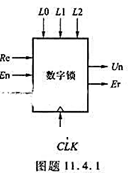

提示:数字锁系统的示意图如图题11.4.1所示,由于开锁过程比较简单,所以没有划分控制单元和处理单元。L0、L1、L2用于从到高位设置密码,另外三个输入端Re,En,Ki中,Re是复位端,当Re=

1时,系统复位进入初始状态;En是控制井关,Ki是数据输入端,当按一下En键使En=1时,从Ki端输入一个数码,再按一下En键,再送一个数码,直到将三个数码送完为止。每输入一个数据都要同原设定的密码比较,依次从低位到高位进行。若相等则准备接收下一位数码,若不相等,系统应进入错误状态。输入数码的位数也是开锁的条件。当输入数码的位数和位值与相应密码都相等时,系统发出开锁信号Un=1,锁被打开,否则Er=1表示开锁过程错误。为保密起见,中间错误状态不显示,并且不能返回初态,直到三个数码全部送完为止。

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

简答题

简答题

微信搜一搜

微信搜一搜

简答题

简答题