题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

三态缓冲门可组成运算器的数据总线,它的输出电平有逻辑“1”或逻辑“0”、高阻抗三种状态。()

三态缓冲门可组成运算器的数据总线,它的输出电平有逻辑“1”或逻辑“0”、高阻抗三种状态。()

提问人:网友18***192

发布时间:2022-01-06

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

三态缓冲门可组成运算器的数据总线,它的输出电平有逻辑“1”或逻辑“0”、高阻抗三种状态。()

更多“三态缓冲门可组成运算器的数据总线,它的输出电平有逻辑“1”或…”相关的问题

更多“三态缓冲门可组成运算器的数据总线,它的输出电平有逻辑“1”或…”相关的问题

三态缓冲门可组成运算器的数据总线,它的输出电平有逻辑“1”、逻辑“0”、浮空三种状态。( )

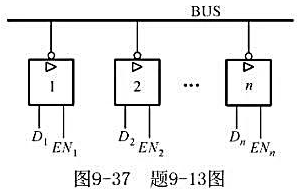

图9-37所示为用三态门传输数据的示意图,图中n个三态门连到总线BUS, 为三态门使能控制端,试说明电路能传输数据的原理。

为三态门使能控制端,试说明电路能传输数据的原理。

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

简答题

简答题

微信搜一搜

微信搜一搜

简答题

简答题