题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

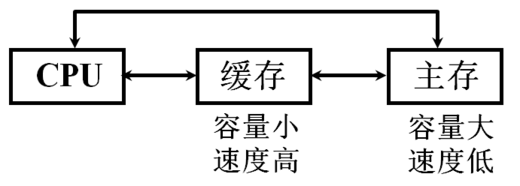

为了提高访存速度,在CPU与cache之间设置一个高速小容量的cache,存放正在执行的程序段,有效地提高

A.写直达法

B.直接地址映像法

C.写回法

D.全相联地址映像法

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.写直达法

B.直接地址映像法

C.写回法

D.全相联地址映像法

更多“为了提高访存速度,在CPU与cache之间设置一个高速小容量…”相关的问题

更多“为了提高访存速度,在CPU与cache之间设置一个高速小容量…”相关的问题

A.Cache的一个地址单元可以存储比主存更多的数据

B.可以使用多个Cache,从而使Cache的总容量与主存相等

C.CPU在执行程序时,访存具有相对的局部性,即程序访问的局部性原理

D.Cache中采用了数据压缩进行存储

A.匹配CPU执行速度与主存存取速度之间的不平衡

B.匹配SRAM与DRAM之间的性能差异

C.扩大CPU的逻辑访存空间

D.实现多任务情况下的存储器管理

在奔腾机主板上的Cache存储器的作用是()。

A.提高硬盘与主存之间的传送速度

B.提高软盘与主存之间的传送速度

C.提高CPU与显示器之间的传送速度

D.提高CPU与主存储器之间的传送速度

A.避免CPU”空等”现象

B.CPU与主存(DRAM)的速度差异

C.程序访问的局部性原理

D.研究人员无聊,自己给自己找事

A. 从功能上看, Cache实质上是CPU寄存器的扩展

B. Cache的存取速度接近于主存的存取速度

C. Cache的主要功能是提高主存与辅存之间的数据交换的速度

D. Cache中的数据是主存很小一部分内容的映射(副本)

A.从功能上看,Cache实质上是CPU寄存器的扩展

B.Cache的存取速度接近于主存的存取速度

C.Cache的主要功能是提高主存与辅存之间数据交换的速度

D.Cache中的数据是主存很小一部分内容的映射(副本)

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

简答题

简答题

微信搜一搜

微信搜一搜

简答题

简答题