题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A. X、Y 两个单元的内容都是 X ⊕y .B. X、Y 两个单元的内容都没有变化C. x、Y 两个单元的内容各位都变反(1变 0,0 变1)D. X、Y 两个单元的内容实现了互换,而没有用临时单元

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

更多“【填空题】巡航控制ECU有两个输入信号:一个是(),另一个是…”相关的问题

更多“【填空题】巡航控制ECU有两个输入信号:一个是(),另一个是…”相关的问题

A. X、Y 两个单元的内容都是 X ⊕y .B. X、Y 两个单元的内容都没有变化C. x、Y 两个单元的内容各位都变反(1变 0,0 变1)D. X、Y 两个单元的内容实现了互换,而没有用临时单元

开始时R键使跑表为零初始状态。在R键无效的时候,按一下S键则计时器开始计时,在此计时状态下,按一下S键暂停计时,再按一下S键则继续计时,并且这一过程可由S键控制重复进行。如果在暂停状态按一下R键,跑表被清零。

如果在计时状态下,按一下R键则暂停计时,再按一下R键则继续计时,并且这一过程也可由R键控制重复进行。当按R键使计时暂停时,再按S键不起作用。

要求跑表的计时范围为0.01s~59min59.99s,计时精度为10ms;跑表的输出能够直接驱动共阳极7段数码管显示。输入信号的频率为100 Hz。

(1)画出跑表的结构框图。

(2)画出控制单元的ASM图及状态图。

(3)用Verilog HDL描述跑表的功能。

设计一个时序电路,只有在连续两个或两个以上时钟作用期间,两个输入信号X1和X0一致时,输出信号才是1,其余情况输出为0。

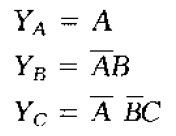

A、设计完成的逻辑图为:

B、设计完成的逻辑图为:

C、真值表为:

D、真值表为:

E、化简后的逻辑函数表达式为:

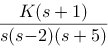

已知单位反馈系统的开环传递函数为 ,其闭环系统稳定的条件是()。

,其闭环系统稳定的条件是()。

A、K>30

B、0<k> <15> C、K>15

D、0 <k> <30>

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

简答题

简答题

微信搜一搜

微信搜一搜

简答题

简答题