题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[单选题]

用Verilog HDL设计门电路时,可以采用( )方法来描述。

A.if语句

B.assign语句

C.case语句

D.loop语句

提问人:网友anonymity

发布时间:2022-01-06

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.if语句

B.assign语句

C.case语句

D.loop语句

更多“用Verilog HDL设计门电路时,可以采用()方法来描述…”相关的问题

更多“用Verilog HDL设计门电路时,可以采用()方法来描述…”相关的问题

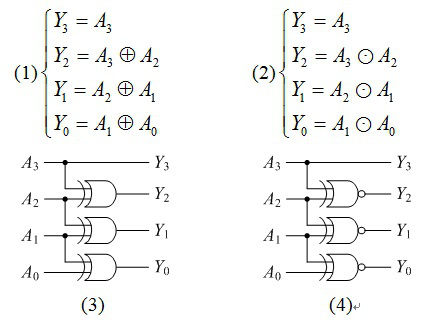

A、(1)和(3)

B、(1)和(4)

C、(2)和(3)

D、(2)和(4)

为了保护您的账号安全,请在“简答题”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

简答题

简答题

微信搜一搜

微信搜一搜

简答题

简答题